Необходимость встраивать высококачественные аналого-цифровые преобразователи в изделия и товары широкого потребления (электробытовые приборы, автомобили, средства телекоммуникации и т. п.), которые всё в большей степени основываются на цифровых технологиях, заставила изготовителей полупроводниковых элементов применить новые подходы к решению проблемы.

В настоящее время за цену менее двадцати долларов можно купить АЦП в корпусе с восемью выводами, причем возможности этих преобразователей могут быть оценены довольно высоко. Их используют, в частности, для работы с самыми современными компонентами — RISC-микроконтроллерами и цифровыми сигнальными процессорами (ЦСП).

Главная особенность таких АЦП состоит в организации управления по одно- или двухпроводной последовательной шине (SPI, Microwire, PC и т. п.), а не через параллельный интерфейс, требующий наличия одного вывода микросхемы на каждый разряд шины управления. Конечно, такой способ передачи битов данных — один за другим по одному проводу — ограничивает скорость обмена информацией, хотя и здесь можно достичь скорости передачи данных порядка 1 Мбит/сек. На практике, с учетом свойств и возможностей схем дискретизации и квантования, не стоит рассчитывать на преодоление барьера в несколько десятков тысяч измерений в секунду, что в среднем соответствует частоте дискретизации 20 кГц.

Таким образом, эти электронные компоненты не стоит сравнивать со сверхскоростными АЦП типа «flash» или «videos», но они, тем не менее, относятся к классу быстродействующих АЦП. Поэтому при разрядности от 8 до 12 бит они прекрасно подходят для решения большинства задач в области создания виртуальных измерительных приборов.

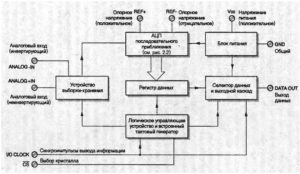

На рис. 2.1 приведена структурная схема стандартных последовательных АЦП, выполненных в корпусах с восемью выводами.

Рис 2.1. Структурная схема последовательного АЦП

Логическое управляющее устройство со встроенным тактовым генератором управляет работой схемы преобразования, функционирующей по принципу последовательного приближения. Этот принцип состоит в постепенном пошаговом накоплении в промежуточном регистре данных двоичного кодового слова, соответствующего соотношению входного аналогового напряжения (разности между уровнями напряжения на дифференциальных входах ANALOG+IN и ANALOG-IN) и опорного напряжения (разности между уровнями напряжения на дифференциальных входах REF+ и REF-).

Цикл преобразования начинается с фиксации уровня входного аналогового напряжения в устройстве выборки-хранения, а затем преобразователь начинает формировать содержимое регистра. Процесс накопления кодового слова занимает некоторое время, называемое временем преобразования.

На практике как минимум один из выводов ANALOG-IN или REF- технологически соединен с общим проводом (GND), вследствие чего лишь некоторые модели последовательных АЦП могут работать по схеме с дифференциальным входом.

По окончании процесса преобразования селектор данных, расположенный перед выходным каскадом, начинает последовательно выбирать биты информации, содержащиеся в регистре данных, и затем также последовательно подает их на выход DATA OUT. Частота выборки и формирования выходных импульсов определяется внешним тактовым сигналом I/O CLOCK.

Для правильного функционирования АЦП необходимо наличие некоторой внешней управляющей системы, которая должна формировать последовательности синхронизирующих сигналов.

В большинстве случаев аналого-цифровое преобразование начинается в момент подачи соответствующего сигнала на вывод /CS (выбор кристалла). Само по себе преобразование выполняется за несколько десятков микросекунд. После этого необходимо подать нужное количество тактовых импульсов на вывод I/O CLOCK, чтобы вывести результат преобразования через вывод DATA OUT. Хотя величина тактовой частоты вывода данных для некоторых моделей имеет ограничение снизу (например, 100 кГц), она все-таки намного ниже, чем внутренняя тактовая частота преобразования. В большинстве случаев скорость последовательного вывода информации зависит только от скорости, с которой управляющая система может обрабатывать поступающие биты данных.

Работа схемы АЦП последовательного приближения (рис. 2.2) заслуживает более подробного описания, так как именно благодаря ей появился этот тип компонентов.

Рис 2.2. Функциональная схема АЦП последовательного приближения с коммутируемой матрицей конденсаторов

Основой функциональной схемы является коммутируемая матрица конденсаторов. Значение каждого бита данных определяется пороговым детектором в зависимости от величины заряда каждого из весовых конденсаторов, составляющих матрицу АЦП. Рис. 2.2 соответствует десятиразрядному АЦП. По рисунку видно, что число конденсаторов, содержащихся в матрице, должно быть на единицу больше, чем число разрядов. Относительный вес каждой цепи матрицы конденсаторов определяется в соответствии с последовательностью степеней числа два, т. е. от 1 до 512 для десятиразрядного АЦП.

В начале цикла преобразования логическое управляющее устройство замыкает все ключи ST и Sc, вследствие чего все конденсаторы одновременно заряжаются до уровня входного напряжения Vi (режим выборки). Затем все ключи размыкаются (режим хранения), и пороговый детектор начинает формировать биты данных, сравнивая напряжение REF- с напряжениями на каждом из конденсаторов матрицы.

Первым обрабатывается напряжение на конденсаторе, установленном в цепи матрицы с максимальным весом (в данном случае — вес 512). Для этого узел 512 подключается к источнику напряжения REF+, а все остальные узлы подключаются к REF-. Если напряжение в суммирующей точке больше порога срабатывания детектора, примерно равного VCC/2, то бит данных устанавливается в нулевое состояние, а узел 512 подключается к источнику напряжения REF-. В противном случае, если напряжение в суммирующей точке меньше порога, бит данных устанавливается в единичное состояние, а узел 512 подключается к источнику REF+ до завершения процесса преобразования. Та же последовательность операций повторяется для цепи с весом 256, потом с весом 128 — и так до тех пор, пока не будет определено значение каждого разряда регистр» данных.

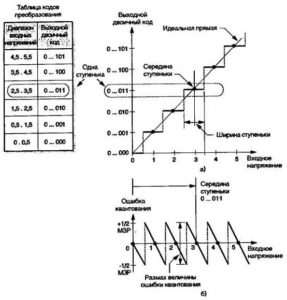

Следует помнить, что n-разрядный АЦП может сформировать лишь 2n различных двоичных кодовых слов (256 для 8 разрядов, 1024 для 10 разрядов, 4096 для 12 разрядов и т. д.). Разница между двумя соседними кодовыми словами соответствует аналоговому весу младшего значащего разряда (МЗР, или LSB в иностранной литературе). Изменение входного напряжения на величину, меньшую по сравнению с этой разницей, может быть не отражено в выходных данных. Некоторые преобразователи, кроме того, вносят дополнительную погрешность и формируют результат с точностью до одного или даже до двух МЗР. Такая дискретность результатов преобразования является следствием характерной для АЦП передаточной характеристики в виде «ступеньки» (рис. 2.3 (а)).

Совершенно очевидно, что в этом случае, так же как при любом другом процессе аналого-цифрового преобразования, полученный результат содержит некоторую ошибку, называемую ошибкой квантования. Причины ее возникновения поясняются в графике, приведенном на рис. 2.3 (б).

Ошибка квантования возникает в результате замены истинной величины отсчета входного сигнала ее дискретным эквивалентом в виде выходного кода и определяется как разность между графиками ступенчатой передаточной характеристики и идеальной прямой. Максимальная величина ошибки для передаточной характеристики, приведенной на рис. 2.3 (а), равна половине величины шага квантования (половине аналогового веса МЗР).

Рис. 2.3. Передаточная характеристике АЦП и таблица кодов преобразования

Важно учитывать эту особенность, которая, если взять для примера 8-разрядный АЦП с полной шкалой 5 В, проявляется в неизбежной погрешности преобразования величиной до 20 мВ. И хотя эта величина составляет лишь 0,4 %, ее следует принимать во внимание.